# UNIT I COMBINATIONAL LOGIC

Combinational Circuits – Analysis and Design Procedures - Binary Adder- Subtractor -Decimal Adder - Binary Multiplier - Magnitude Comparator - Decoders – Encoders – Multiplexers - Introduction to HDL – HDL Models of Combinational circuits.

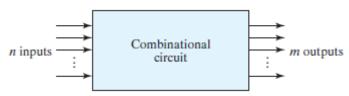

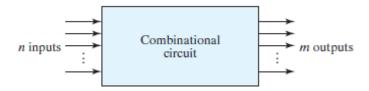

# **COMBINATIONAL CIRCUITS**

- ✤ A combinational circuit consists of logic gates whose outputs at any time are determined from only the present combination of inputs.

- ✤ A combinational circuit performs an operation that can be specified logically by a set of Boolean functions.

# Sequential circuits:

- Sequential circuits employ storage elements in addition to logic gates. Their outputs are a function of the inputs and the state of the storage elements.

- Because the state of the storage elements is a function of previous inputs, the outputs of a sequential circuit depend not only on present values of inputs, but also on past inputs, and the circuit behavior must be specified by a time sequence of inputs and internal states.

# ANALYSIS PROCEDURE

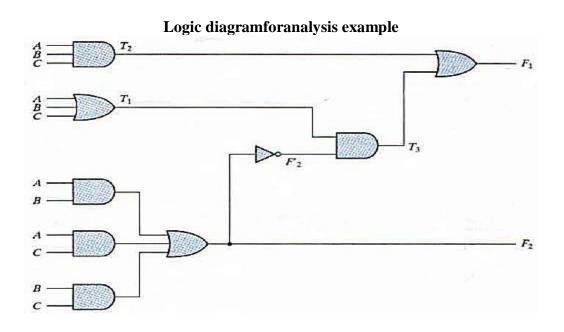

# Explain the analysis procedure. Analyze the combinational circuit the following logic diagram.

(May

# 2015)

- The analysis of a combinational circuit requires that we determine the function that the circuit implements.

- The analysis can be performed manually by finding the Boolean functions or truth table or by using a computer simulation program.

- The first step in the analysis is to make that the given circuit is combinational or sequential.

- Once the logic diagram is verified to be combinational, one can proceed to obtain the output Boolean functions or the truth table.

- ✤ To obtain the output Boolean functions from a logic diagram,

- ✓ Label all gate outputs that are a function of input variables with arbitrary symbols or names. Determine the Boolean functions for each gate output.

- ✓ Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols or names. Find the Boolean functions for these gates.

- $\checkmark$  Repeat the process in step 2 until the outputs of the circuit are obtained.

- ✓ By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

The Boolean functions for the above outputs are,

$$F_2 = AB + AC + BC$$

$$T_1 = A + B + C$$

$$T_2 = ABC$$

Next, we consider outputs of gates that are a function of already defined symbols:

$$T_3 = F'_2 T_1$$

$$F_1 = T_3 + T_2$$

To obtain  $F_1$  as a function of A, B, and C, we form a series of substitutions as follows:

$$F_{1} = T_{3} + T_{2} = F'_{2}T_{1} + ABC = (AB + AC + BC)'(A + B + C) + ABC$$

=  $(A' + B')(A' + C')(B' + C')(A + B + C) + ABC$

=  $(A' + B'C')(AB' + AC' + BC' + B'C) + ABC$

=  $A'BC' + A'B'C + AB'C' + ABC$

Proceed to obtain the truth table for the outputs of those gates which are a function of previously defined values until the columns for all outputs are determined.

| A | B | C | F2  | F'2 | <i>T</i> <sub>1</sub> | T2 | <i>T</i> <sub>3</sub> | F |

|---|---|---|-----|-----|-----------------------|----|-----------------------|---|

| 0 | 0 | 0 | 0   | 1   | 0                     | 0  | 0                     | 0 |

| 0 | 0 | 1 | 0   | 1   | 1                     | 0  | 1                     | 1 |

| 0 | 1 | 0 | 0   | 1   | 1                     | 0  | 1                     | 1 |

| 0 | 1 | 1 | 1   | 0   | 1                     | 0  | 0                     | 0 |

| 1 | 0 | 0 | 0   | 1   | 1                     | 0  | 1                     | 1 |

| 1 | 0 | 1 | 1   | 0   | 1                     | 0  | 0                     | 0 |

| 1 | 1 | 0 | 1 1 | 0   | 1                     | 0  | 0                     | 0 |

| 1 | 1 | 1 | 1   | 0   | 1                     | 1  | 0                     | 1 |

Page 2

# DESIGNPROCEDURE

# Explain the procedure involved in designing combinational circuits.

- The design of combinational circuits starts from the specification of the design objective and culminates in a logic circuit diagram or a set of Boolean functions from which the logic diagram can be obtained.

- ✤ The procedure involved involves the following steps,

- ✓ From the specifications of the circuit, determine the required number of inputs and outputs and assign a symbol to each.

- $\checkmark$  Derive the truth table that defines the required relationship between inputs and outputs.

- $\checkmark$  Obtain the simplified Boolean functions for each output as a function of the input variables.

- $\checkmark$  Draw the logic diagram and verify the correctness of the design.

#### \*\*\*\*\*\*

# CIRCUITS FOR ARITHMETIC OPERATIONS

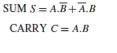

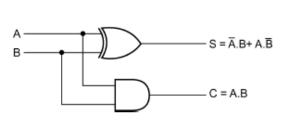

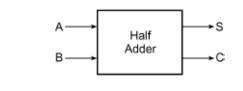

# Half adder:

Construct a half adder with necessary diagrams.

(Nov-06, May- 07)

- A half-adder is an arithmetic circuit block that can be used to add two bits and produce two outputs SUM and CARRY.

- The Boolean expressions for the SUM and CARRY outputs are given by the equations

# Truth Table:

| А | В | s | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

# Logic Diagram:

Half adder using NAND gate:

\*\*\*\*\*

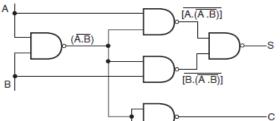

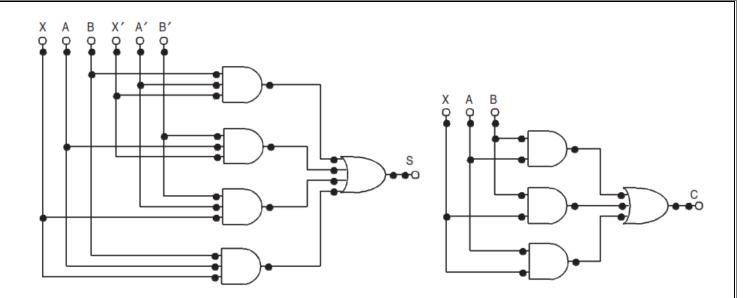

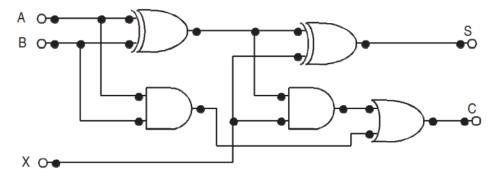

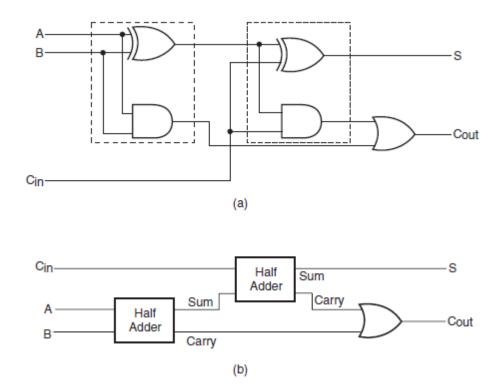

# Full adder:

Design a full adder using NAND and NOR gates respectively.

- (Nov -10)

- ✤ A Full-adder is an arithmetic circuit block that can be used to add three bits and produce two outputs SUM and CARRY.

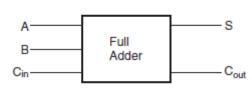

- ✤ The Boolean expressions for the SUM and CARRY outputs are given by the equations

$$\begin{split} S &= \overline{A}.\overline{B}.C_{\text{in}} + \overline{A}.B.\overline{C}_{\text{in}} + A.\overline{B}.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \\ C_{\text{out}} &= B.C_{\text{in}} + A.B + A.C_{\text{in}} \end{split}$$

#### Truth table:

|   | Input variables |   | Outputs |   |  |

|---|-----------------|---|---------|---|--|

| X | A               | В | S       | С |  |

| 0 | 0               | 0 | 0       | 0 |  |

| 0 | 0               | 1 | 1       | 0 |  |

| 0 | 1               | 0 | 1       | 0 |  |

| 0 | 1               | 1 | 0       | 1 |  |

| 1 | 0               | 0 | 1       | 0 |  |

| 1 | 0               | 1 | 0       | 1 |  |

| 1 | 1               | 0 | 0       | 1 |  |

| 1 | 1               | 1 | 1       | 1 |  |

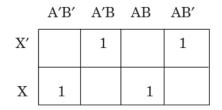

#### Karnaugh map:

K-Map for Sum

K-Map for Carry

✤ The simplified Boolean expressions of the outputs are

S = X'A'B + X'AB' + XA'B' + XABC = AB + BX + AX

#### Logic diagram:

✤ The Boolean expressions of S and C are modified as follows

$$S = X'A'B + X'AB' + XA'B' + XAB$$

= X' (A'B + AB') + X (A'B' + AB)

= X' (A  $\oplus$  B) + X (A  $\oplus$  B)'

= X  $\oplus$  A  $\oplus$  B

C = AB + BX + AX = AB + X (A + B)

= AB + X (AB + AB' + AB + A'B)

= AB + X (AB + AB' + A'B)

= AB + XAB + X (AB' + A'B)

= AB + X (A  $\oplus$  B)

# Full adder using Two half adder:

✤ Logic diagram according to the modified expression is shown Figure.

\*\*\*\*\*

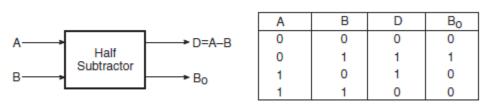

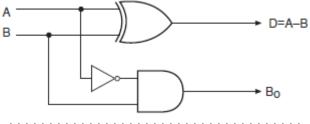

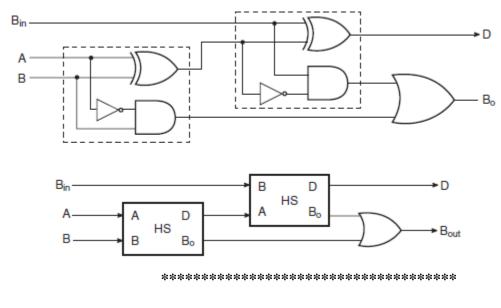

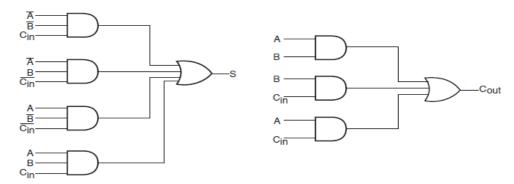

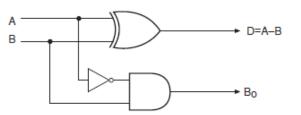

Half subtractor: Design a half subtractor circuit.

(Nov-2009)

- ✤ A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output.

- The BORROW output here specifies whether a '1' has been borrowed to perform the subtraction. The Boolean expression for difference and borrow is:

$$D = \overline{A}.B + A.\overline{B}$$

$$B_0 = \overline{A}.B$$

#### Logic diagram:

#### \*\*\*\*\*\*

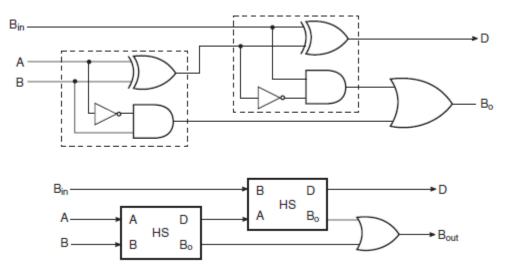

#### Full subtractor:

#### Design a full subtractor.

#### (Nov-2009,07)

- A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a '1' has already been borrowed by the previous adjacent lower minuend bit or not.

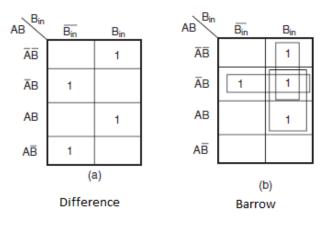

- ✤ As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin .

- There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo. The BORROW output bit tells whether the minuend bit needs to borrow a '1' from the next possible higher minuend bit. The Boolean expression for difference and barrow is:

$D = \overline{A.B.B_{in}} + \overline{A.B.B_{in}} + A.\overline{B.B_{in}} + A.B.B_{in}$  $B_0 = \overline{A.B} + \overline{A.B_{in}} + B.B_{in}$

|        | Minuend<br>(A) | Subtrahend<br>(B) | Borrow<br>In (Bin) | Difference<br>(D) | Borrow<br>Out (B <sub>0</sub> ) |

|--------|----------------|-------------------|--------------------|-------------------|---------------------------------|

|        | 0              | 0                 | 0                  | 0                 | 0                               |

|        | 0              | 0                 | 1                  | 1                 | 1                               |

|        | 0              | 1                 | 0                  | 1                 | 1                               |

| B Full | 0              | 1                 | 1                  | 0                 | 1                               |

| Bin    | 1              | 0                 | 0                  | 1                 | 0                               |

|        | 1              | 0                 | 1                  | 0                 | 0                               |

|        | 1              | 1                 | 0                  | 0                 | 0                               |

|        | 1              | 1                 | 1                  | 1                 | 1                               |

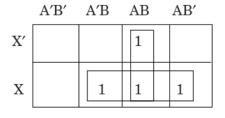

K-Map:

Full subtractor using two half subtractor:

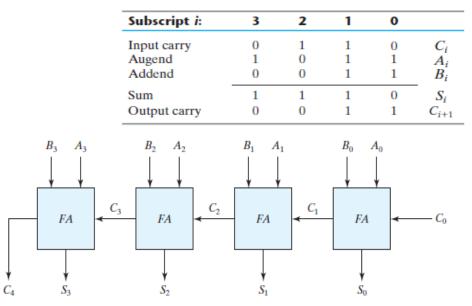

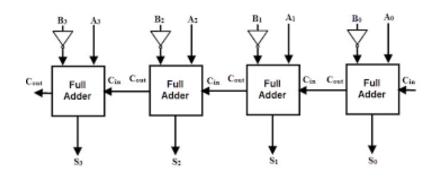

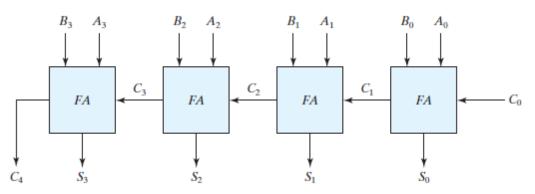

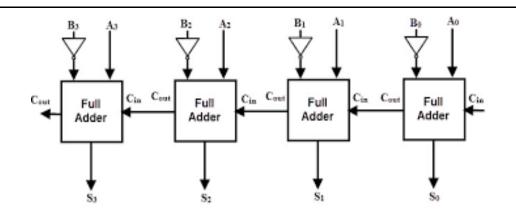

Parallel Binary Adder: (Ripple Carry Adder):

# Explain about four bit adder. (or) Design of 4 bit binary adder – subtractor circuit. (Apr – 2019)

- A binary adder is a digital circuit that produces the arithmetic sum of two binary numbers. It can be constructed with full adders connected in cascade, with the output carry from each full adder connected to the input carry of the next full adder in the chain.

- Addition of n-bit numbers requires a chain of n- full adders or a chain of one-half adder and n-1 full adders. In the former case, the input carry to the least significant position is fixed at 0.

- Figure shows the interconnection of four full-adder (FA) circuits to provide a four-bit binary ripple carry adder.

- The carries are connected in a chain through the full adders. The input carry to the adder is C0, and it ripples through the full adders to the output carry C4. The S outputs generate the required sum bits.

**Example:** Consider the two binary numbers A = 1011 and B = 0011. Their sum S = 1110 is formed with the four-bit adder as follows:

- ✓ The carry output of lower order stage is connected to the carry input of the next higher order stage. Hence this type of adder is called ripple carry adder.

- ✓ In a 4-bit binary adder, where each full adder has a propagation delay of tp ns, the output in the fourth stage will be generated only after 4tp ns.

- $\checkmark$  The magnitude of such delay is prohibitive for high speed computers.

- ✓ One method of speeding up this process is look-ahead carry addition which eliminates ripple carry delay.

\*\*\*\*\*

#### **Complement of a number:**

#### 1's complement:

The 1's complement of a binary number is formed by changing 1 to 0 and 0 to 1.

#### **Example:**

- 1. The 1's complement of 1011000 is 0100111.

- 2. The 1's complement of 0101101 is 1010010.

#### 2's complement:

The 2's complement of a binary number is formed by adding 1 with 1's complement of a binary number.

#### **Example:**

- 1. The 2's complement of 1101100 is 0010100

- 2. The 2's complement of 0110111 is 1001001

# Subtraction using 2's complement addition:

- $\checkmark$  The subtraction of unsigned binary number can be done by means of complements.

- ✓ Subtraction of A-B can be done by taking 2's complement of B and adding it to A.

- $\checkmark$  Check the resulting number. If carry present, the number is positive and remove the carry.

- ✓ If no carry present, the resulting number is negative, take the 2's complement of result and put negative sign.

# Example:

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction

(a) X - Y and (b) Y - X by using 2's complements.

**Solution:** (a) *X* = 1010100 2's complement of *Y* = + 0111101 Sum= 10010001 Discard end carry. *Answer*: *X* - *Y* = 0010001

(b) Y = 1000011

2's complement of X = +0101100

Sum= 1101111

There is no end carry. Therefore, the answer is Y - X = -(2's complement of 1101111) = -0010001.

#### \*\*\*\*\*

# Parallel Binary Subtractor:

- ✓ The subtraction of unsigned binary numbers can be done most conveniently by means of complements. The subtraction A B can be done by taking the 2's complement of B and adding it to A. The 2's complement can be obtained by taking the 1's complement and adding 1 to the least significant pair of bits. The 1's complement can be implemented with inverters, and a 1 can be added to the sum through the input carry.

- ✓ The circuit for subtracting A B consists of an adder with inverters placed betweeneach data input B and the corresponding input of the full adder. The input carry *C*in mustbe equal to 1 when subtraction is

performed. The operation thus performed becomes A, plus the 1's complement of B, plus 1. This is equal to A plus the 2's complement of B.

✓ For unsigned numbers, that gives *A*-*B* if *A*>=*B* or the 2's complement of *B* - *A*if *A* <*B*. For signed numbers, the result is *A* - *B*, provided that there is no overflow.

#### \*\*\*\*\*

#### Fast adder (or) Carry Look Ahead adder: Design a carry look ahead adder circuit.

(Nov-2010)

- The carry look ahead adder is based on the principle of looking at the lower order bits of the augend and addend to see if a higher order carry is to be generated.

- ✤ It uses two functions carry generate and carry propagate.

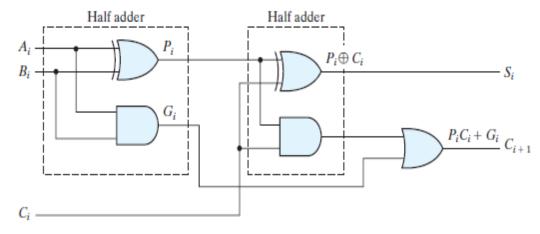

Consider the circuit of the full adder shown in Fig. If we define two new binaryvariables

$$P_i = A_i \oplus B_i$$

$$G_i = A_i B_i$$

the output sum and carry can respectively be expressed as

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_i C_i$$

Gi is called a carry generate, and it produces a carry of 1 when both Ai and Bi are 1, regardless of the input carry Ci. Pi is called a carry propagate, because it determines whether a carry into stage i will propagate into stage i + 1 (i.e., whether an assertion of Ci will propagate to an assertion of Ci+1).

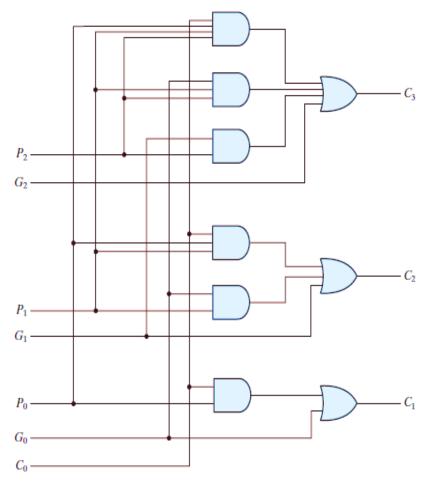

We now write the Boolean functions for the carry outputs of each stage and substitute the value of each Ci from the previous equations:

$$C_{0} = \text{input carry}$$

$$C_{1} = G_{0} + P_{0}C_{0}$$

$$C_{2} = G_{1} + P_{1}C_{1} = G_{1} + P_{1}(G_{0} + P_{0}C_{0}) = G_{1} + P_{1}G_{0} + P_{1}P_{0}C_{0}$$

$$C_{3} = G_{2} + P_{2}C_{2} = G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0} = P_{2}P_{1}P_{0}C_{0}$$

Logic diagram of carry lookahead generator

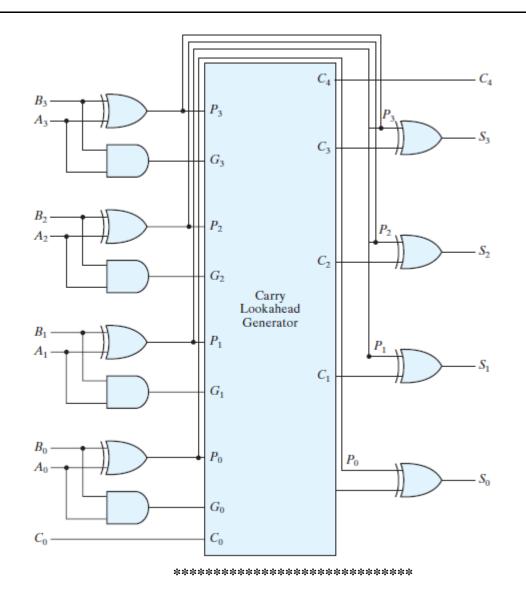

- ✤ The construction of a four-bit adder with a carry lookahead scheme is shown in Fig.

- Each sum output requires two exclusive-OR gates.

- The output of the first exclusive-OR gate generates the Pi variable, and the AND gate generates the Gi variable.

- The carries are propagated through the carry look ahead generator and applied as inputs to the second exclusive-OR gate.

- ✤ All output carries are generated after a delay through two levels of gates.

- Thus, outputs S1 through S3 have equal propagation delay times. The two-level circuit for the output carry C4 is not shown. This circuit can easily be derived by the equation-substitution method.

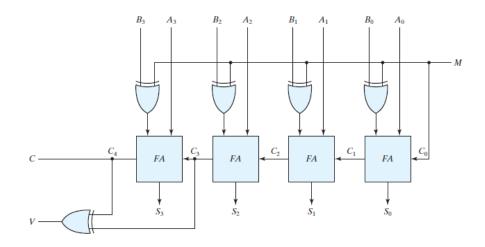

# 4 bit-Parallel adder/subtractor:

# Explain about binary parallel / adder subtractor. [NOV - 2019]

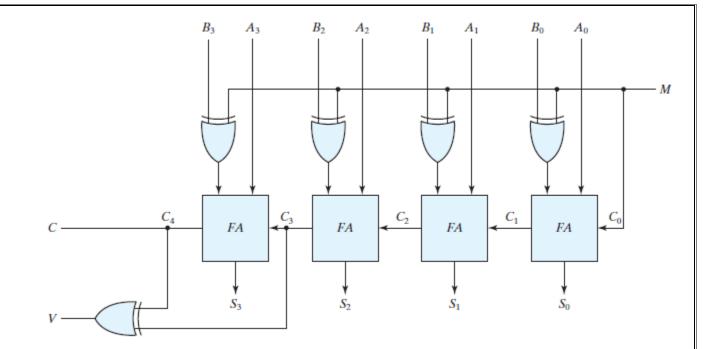

- The addition and subtraction operations can be combined into one circuit with one common binary adder by including an exclusive-OR gate with each full adder. A four-bit adder–subtractor circuit is shown in Fig.

- ★ The mode input *M* controls the operation. When M = 0, the circuit is an adder, and when M = 1, the circuit becomes a subtractor.

- ✤ It performs the operations of both addition and subtraction.

- It has two 4bit inputs  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$ .

- ✤ The mode input M controls the operation when M=0 the circuit is an adder and when M=1 the circuits become subtractor.

- $\clubsuit$  Each exclusive-OR gate receives input *M* and one of the inputs of *B*.

- ↔ When M = 0, we have B xor0 = B. The full adders receive the value of B, the input carry is 0, and the circuit performs A plus B. This results in sum S<sub>3</sub>S<sub>2</sub>S<sub>1</sub>S<sub>0</sub>and carry C<sub>4</sub>.

- ♦ When M = 1, we have B xor 1 = B' and  $C_0 = 1$ . The B inputs are all complemented and a 1 is added through the input carry thus producing 2's complement of B.

- ♦ Now the data  $A_3A_2A_1A_0$  will be added with 2's complement of  $B_3B_2B_1B_0$  to produce the sum i.e., A-B if A≥B or the 2's complement of B-A if A<B.

#### \*\*\*\*\*

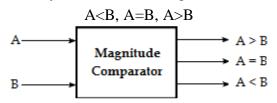

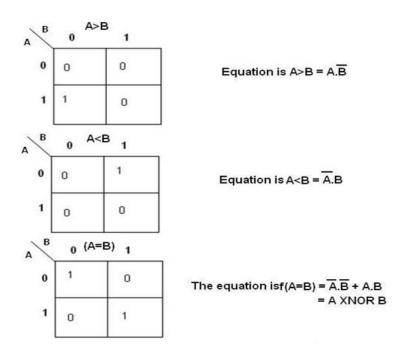

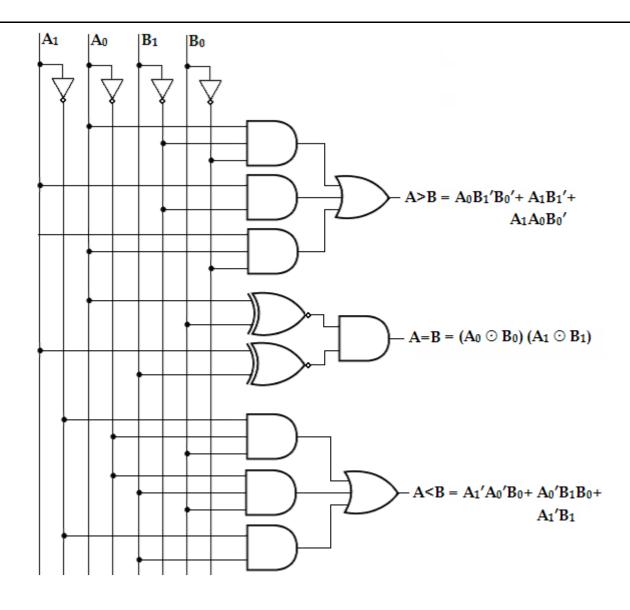

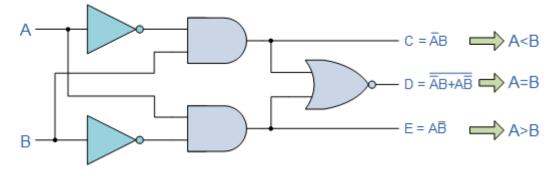

#### Comparators

Design a 2 bit magnitude comparator.

(May 2006)

It is a combinational circuit that compares two numbers and determines their relative magnitude. The output of comparator is usually 3 binary variables indicating:

**1-bitcomparator:** Let's begin with 1bit comparator and from the name we can easily make out that this circuit would be used to compare 1bit binary numbers.

| Α | В | A>B | A=B | A <b< th=""></b<> |

|---|---|-----|-----|-------------------|

| 0 | 0 | 0   | 1   | 0                 |

| 1 | 0 | 1   | 0   | 0                 |

| 0 | 1 | 0   | 0   | 1                 |

| 1 | 1 | 0   | 1   | 0                 |

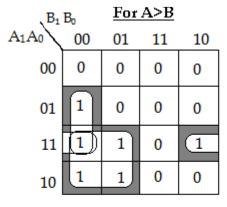

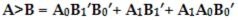

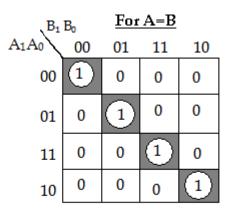

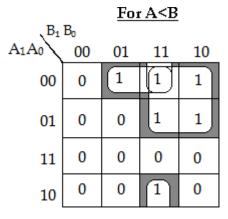

For a 2-bit comparator we have four inputs A1 A0 and B1 B0 and three output E (is 1 if two numbers are equal) G (is 1 when A>B) and L (is 1 when A<B) If we use truth table and K-map the result is

# **Design of 2 – bit Magnitude Comparator.**

The truth table of 2-bit comparator is given in table below

#### Truth table:

|    | Inp | outs |                | Outputs |     |                   |  |

|----|-----|------|----------------|---------|-----|-------------------|--|

| A3 | A2  | A1   | A <sub>0</sub> | A>B     | A=B | A <b< th=""></b<> |  |

| 0  | 0   | 0    | 0              | 0       | 1   | 0                 |  |

| 0  | 0   | 0    | 1              | 0       | 0   | 1                 |  |

| 0  | 0   | 1    | 0              | 0       | 0   | 1                 |  |

| 0  | 0   | 1    | 1              | 0       | 0   | 1                 |  |

| 0  | 1   | 0    | 0              | 1       | 0   | 0                 |  |

| 0  | 1   | 0    | 1              | 0       | 1   | 0                 |  |

| 0  | 1   | 1    | 0              | 0       | 0   | 1                 |  |

| 0  | 1   | 1    | 1              | 0       | 0   | 1                 |  |

| 1  | 0   | 0    | 0              | 1       | 0   | 0                 |  |

| 1  | 0   | 0    | 1              | 1       | 0   | 0                 |  |

| 1  | 0   | 1    | 0              | 0       | 1   | 0                 |  |

| 1  | 0   | 1    | 1              | 0       | 0   | 1                 |  |

| 1  | 1   | 0    | 0              | 1       | 0   | 0                 |  |

| 1  | 1   | 0    | 1              | 1       | 0   | 0                 |  |

| 1  | 1   | 1    | 0              | 1       | 0   | 0                 |  |

| 1  | 1   | 1    | 1              | 0       | 1   | 0                 |  |

#### K-Map:

$\begin{aligned} \mathbf{A} &= \mathbf{B} = \mathbf{A}_{1}' \mathbf{A}_{0}' \mathbf{B}_{1}' \mathbf{B}_{0}' + \mathbf{A}_{1}' \mathbf{A}_{0} \mathbf{B}_{1}' \mathbf{B}_{0} + \\ \mathbf{A}_{1} \mathbf{A}_{0} \mathbf{B}_{1} \mathbf{B}_{0} + \mathbf{A}_{1} \mathbf{A}_{0}' \mathbf{B}_{1} \mathbf{B}_{0}' \\ &= \mathbf{A}_{1}' \mathbf{B}_{1}' \left( \mathbf{A}_{0}' \mathbf{B}_{0}' + \mathbf{A}_{0} \mathbf{B}_{0} \right) + \mathbf{A}_{1} \mathbf{B}_{1} \left( \mathbf{A}_{0} \mathbf{B}_{0} + \mathbf{A}_{0}' \mathbf{B}_{0}' \right) \\ &= \left( \mathbf{A}_{0} \odot \mathbf{B}_{0} \right) \left( \mathbf{A}_{1} \odot \mathbf{B}_{1} \right) \end{aligned}$

$A \le B = A_1 A_0 B_0 + A_0 B_1 B_0 + A_1 B_1$ Logic Diagram:

#### 4 bit magnitude comparator:

Design a 4 bit magnitude comparators. (Apr – 2019)

Input

$$A = A_3 A_2 A_1 A_0$$

$$B = B_3 B_2 B_1 B_0$$

**Function Equation**

$$(A = B) = x_3x_2x_1x_0$$

$$(A > B) = A_3B_3' + x_3A_2B_2' + x_3x_2A_1B_1' + x_3x_2x_1A_0B_0'$$

$$(A < B) = A_3B_3 + x_3A_2B_2 + x_3x_2A_1B_1' + x_3x_2x_1A'n_0B_0'$$

Four-bit magnitude comparator

\*\*\*\*\*

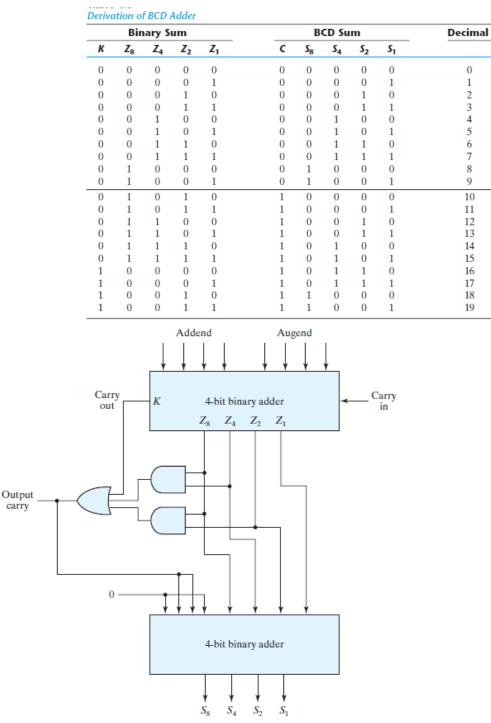

#### **BCD Adder:**

Design to perform BCD addition.(or) What is BCD adder? Design an adder to perform arithmetic addition of two decimal bits in BCD. (May -08)(Apr 2017,2018)[Nov - 2019]

-(A = B)

- Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 9 + 9 + 1 = 19, the 1 in the sum being an input carry.

- Suppose we apply two BCD digits to a four-bit binary adder. The adder will form the sum in binary and produce a result that ranges from 0 through 19. These binary numbers are listed in Table and are labeled by symbols K, Z8, Z4, Z2, and Z1. K is the carry, and the subscripts under the letter Z represent the weights 8, 4, 2, and 1 that can be assigned to the four bits in the BCD code.

✤ A BCD adder that adds two BCD digits and produces a sum digit in BCD is shown in Fig. The two decimal digits, together with the input carry, are first added in the top four-bit adder to produce the binary sum.

- When the output carry is equal to 0, nothing is added to the binary sum. When it is equal to 1, binary 0110 is added to the binary sum through the bottom four-bit adder.

- The condition for a correction and an output carry can be expressed by the Boolean function

$\mathbf{C} = \mathbf{K} + \mathbf{Z}\mathbf{8}\mathbf{Z}\mathbf{4} + \mathbf{Z}\mathbf{8}\mathbf{Z}\mathbf{2}$

- The output carry generated from the bottom adder can be ignored, since it supplies information already available at the output carry terminal.

- ✤ A decimal parallel adder that adds n decimal digits needs n BCD adder stages. The output carry from one stage must be connected to the input carry of the next higher order stage.

\*\*\*\*\*

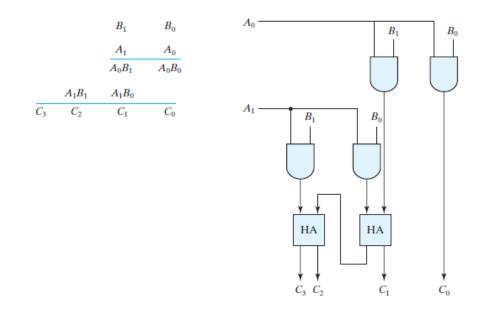

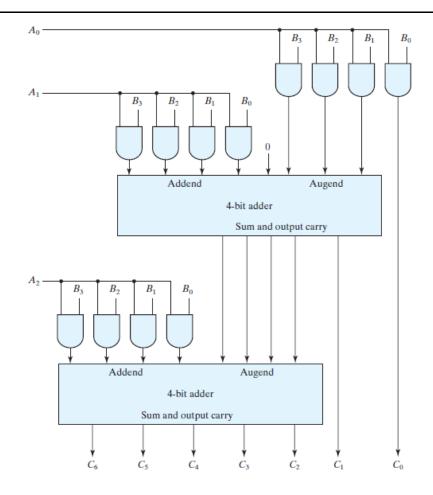

#### **Binary Multiplier:** *Explain about binary Multiplier.*

- Multiplication of binary numbers is performed in the same way as multiplication of decimal numbers. The multiplicand is multiplied by each bit of the multiplier, starting from the least significant bit. Each such multiplication forms a partial product.

- Successive partial products are shifted one position to the left. The final product is obtained from the sum of the partial products.

- A combinational circuit binary multiplier with more bits can be constructed in a similar fashion.

- ✤ A bit of the multiplier is ANDed with each bit of the multiplicand in as many levels as there are bits in the multiplier.

- The binary output in each level of AND gates is added with the partial product of the previous level to form a new partial product. The last level produces the product.

\*\*\*\*\*

# **CODE CONVERSION**

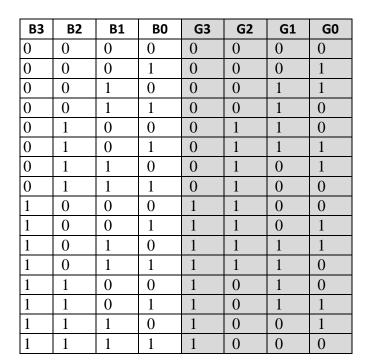

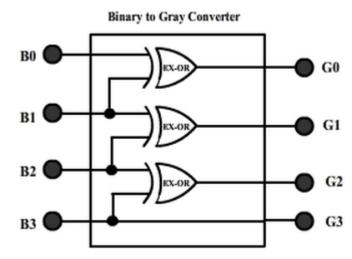

Design a binary to gray converter.

(Nov-2009)(Nov

Page 20

#### Page 21

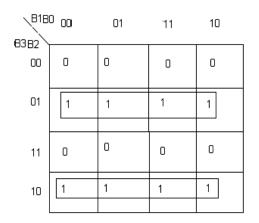

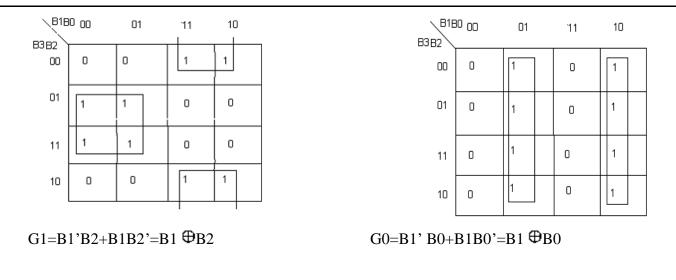

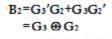

# G2=B3'B2+B3B2'=B3 ⊕B2

2017)

**Truth Table**

**Binary to Grayconverter**

Gray code is unit distance code. Input code: Binary  $[B_3 \ B_2 \ B_1 \ B_0]$ output code: Gray  $[G_3 G_2 G_1 G_0]$

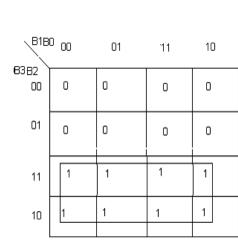

# **K-MAP FORG2:**

**K-MAP FORG0:**

#### Logic diagram:

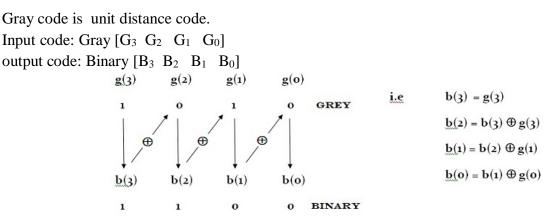

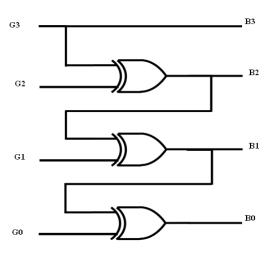

#### Gray to Binary converter:

Design a gray to binary converter.(OR) Design a combinational circuit that converts a four bit gray code to a four bit binary number using exclusive – OR gates. (Nov-2009) [NOV – 2019]

**Truth Table:**

|    | Gray | code |    |    | Natural-binary code |    |    |  |  |

|----|------|------|----|----|---------------------|----|----|--|--|

| G3 | G2   | G1   | G0 | B3 | B2                  | B1 | BO |  |  |

|    |      |      |    |    |                     |    |    |  |  |

| 0  | 0    | 0    | 0  | 0  | 0                   | 0  | 0  |  |  |

| 0  | 0    | 0    | 1  | 0  | 0                   | 0  | 1  |  |  |

| 0  | 0    | 1    | 0  | 0  | 0                   | 1  | 1  |  |  |

| 0  | 0    | 1    | 1  | 0  | 0                   | 1  | 0  |  |  |

| 0  | 1    | 0    | 0  | 0  | 1                   | 1  | 1  |  |  |

| 0  | 1    | 0    | 1  | 0  | 1                   | 1  | 0  |  |  |

| 0  | 1    | 1    | 0  | 0  | 1                   | 0  | 0  |  |  |

| 0  | 1    | 1    | 1  | 0  | 1                   | 0  | 1  |  |  |

| 1  | 0    | 0    | 0  | 1  | 1                   | 1  | 1  |  |  |

| 1  | 0    | 0    | 1  | 1  | 1                   | 1  | 0  |  |  |

| 1  | 0    | 1    | 0  | 1  | 1                   | 0  | 0  |  |  |

| 1  | 0    | 1    | 1  | 1  | 1                   | 0  | 1  |  |  |

| 1  | 1    | 0    | 0  | 1  | 0                   | 0  | 0  |  |  |

| 1  | 1    | 0    | 1  | 1  | 0                   | 0  | 1  |  |  |

| 1  | 1    | 1    | 0  | 1  | 0                   | 1  | 1  |  |  |

| 1  | 1    | 1    | 1  | 1  | 0                   | 1  | 0  |  |  |

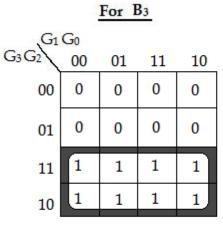

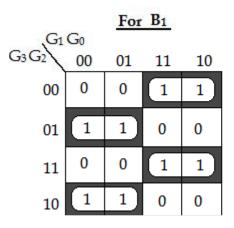

# K-Map:

For B<sub>2</sub>

| G3 G2 | G <sub>0</sub> | 01 | 11 | 10 |

|-------|----------------|----|----|----|

| 00    | 0              | 0  | 0  | 0  |

| 01    | 1              | 1  | 1  | 1  |

| 11    | 0              | 0  | 0  | 0  |

| 10    | 1              | 1  | 1  | 1  |

10

| 00 | 0 | 1 | 0 | 1 |

|----|---|---|---|---|

| 01 | 1 | 0 | 1 | 0 |

| 11 | 0 | 1 | 0 | 1 |

| 10 | 1 | 0 | 1 | 0 |

## Logic Diagram:

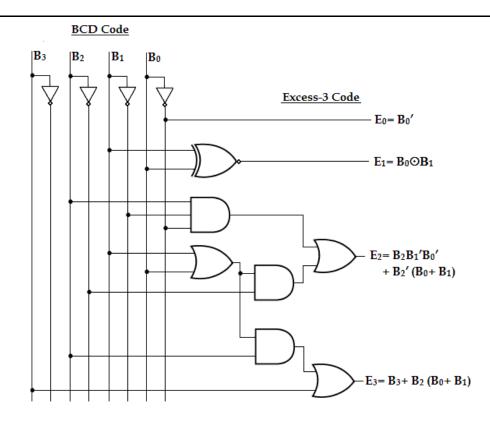

# BCD to Excess -3 converter:

Design a combinational circuits to convert binary coded decimal number into an excess-3 code.

Excess-3 code is modified form of BCD code.

(Nov-06,09,10, May-08,10)

• Excess -3 code is derived from BCD code by adding 3to each coded number.

#### Truth table:

|         |                       | BCD            | code           |                |                | Excess         | -3 code |                |

|---------|-----------------------|----------------|----------------|----------------|----------------|----------------|---------|----------------|

| Decimal | <b>B</b> <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> | E <sub>3</sub> | E <sub>2</sub> | E1      | E <sub>0</sub> |

| 0       | 0                     | 0              | 0              | 0              | 0              | 0              | 1       | 1              |

| 1       | 0                     | 0              | 0              | 1              | 0              | 1              | 0       | 0              |

| 2       | 0                     | 0              | 1              | 0              | 0              | 1              | 0       | 1              |

| 3       | 0                     | 0              | 1              | 1              | 0              | 1              | 1       | 0              |

| 4       | 0                     | 1              | 0              | 0              | 0              | 1              | 1       | 1              |

| 5       | 0                     | 1              | 0              | 1              | 1              | 0              | 0       | 0              |

| 6       | 0                     | 1              | 1              | 0              | 1              | 0              | 0       | 1              |

| 7       | 0                     | 1              | 1              | 1              | 1              | 0              | 1       | 0              |

| 8       | 1                     | 0              | 0              | 0              | 1              | 0              | 1       | 1              |

| 9       | 1                     | 0              | 0              | 1              | 1              | 1              | 0       | 0              |

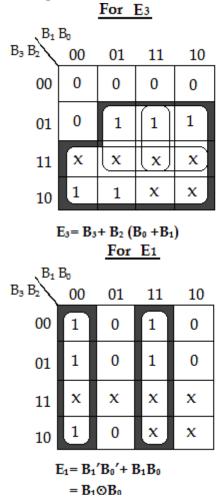

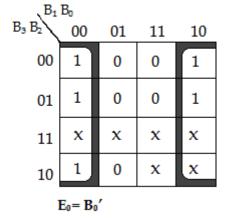

B<sub>1</sub> B<sub>0</sub>

K-Map:

$E_2 = B_2 B_1' B_0' + B_2' (B_0 + B_1)$ For E<sub>0</sub>

Logic Diagram

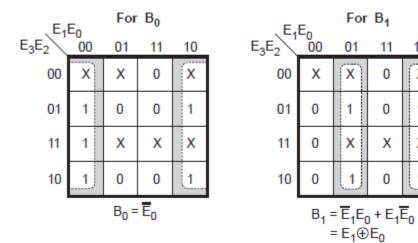

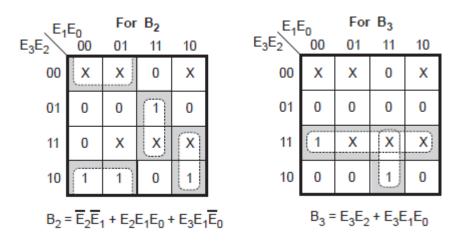

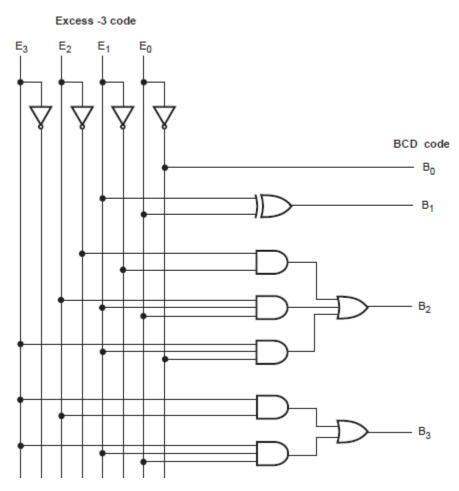

# Excess -3 to BCD converter:

Design a combinational circuit to convert Excess-3 to BCD code.

(May 2007)

#### Truth table:

| Destand |                | Excess         | -3 code        |                | BCD code       |                       |                |                |

|---------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|

| Decimal | E <sub>3</sub> | E <sub>2</sub> | E <sub>1</sub> | E <sub>0</sub> | B <sub>3</sub> | <b>B</b> <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |

| 3       | 0              | 0              | 1              | 1              | 0              | 0                     | 0              | 0              |

| 4       | 0              | 1              | 0              | 0              | 0              | 0                     | 0              | 1              |

| 5       | 0              | 1              | 0              | 1              | 0              | 0                     | 1              | 0              |

| 6       | 0              | 1              | 1              | 0              | 0              | 0                     | 1              | 1              |

| 7       | 0              | 1              | 1              | 1              | 0              | 1                     | 0              | 0              |

| 8       | 1              | 0              | 0              | 0              | 0              | 1                     | 0              | 1              |

| 9       | 1              | 0              | 0              | 1              | 0              | 1                     | 1              | 0              |

| 10      | 1              | 0              | 1              | 0              | 0              | 1                     | 1              | 1              |

| 11      | 1              | 0              | 1              | 1              | 1              | 0                     | 0              | 0              |

| 12      | 1              | 1              | 0              | 0              | 1              | 0                     | 0              | 1              |

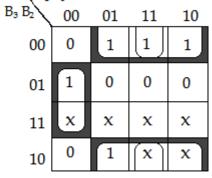

#### K-map simplification

10

Х

1

Х

1

# Logic diagram

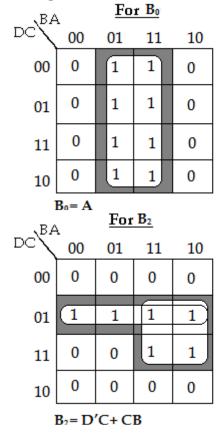

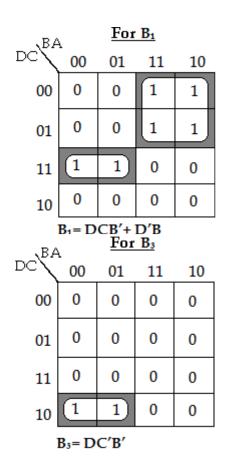

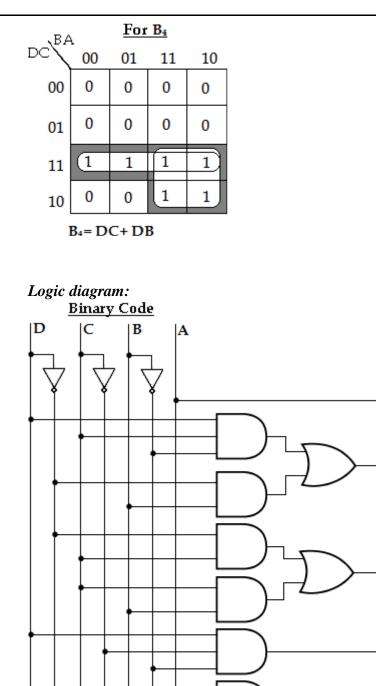

Design Binary to BCD converter.

#### Truth table:

| D . 1   |   | Binary | y Code |   |                | В                     | CD Cod         | e  |                |

|---------|---|--------|--------|---|----------------|-----------------------|----------------|----|----------------|

| Decimal | D | С      | В      | Α | B <sub>4</sub> | <b>B</b> <sub>3</sub> | B <sub>2</sub> | B1 | B <sub>0</sub> |

| 0       | 0 | 0      | 0      | 0 | 0              | 0                     | 0              | 0  | 0              |

| 1       | 0 | 0      | 0      | 1 | 0              | 0                     | 0              | 0  | 1              |

| 2       | 0 | 0      | 1      | 0 | 0              | 0                     | 0              | 1  | 0              |

| 3       | 0 | 0      | 1      | 1 | 0              | 0                     | 0              | 1  | 1              |

| 4       | 0 | 1      | 0      | 0 | 0              | 0                     | 1              | 0  | 0              |

| 5       | 0 | 1      | 0      | 1 | 0              | 0                     | 1              | 0  | 1              |

| 6       | 0 | 1      | 1      | 0 | 0              | 0                     | 1              | 1  | 0              |

| 7       | 0 | 1      | 1      | 1 | 0              | 0                     | 1              | 1  | 1              |

| 8       | 1 | 0      | 0      | 0 | 0              | 1                     | 0              | 0  | 0              |

| 9       | 1 | 0      | 0      | 1 | 0              | 1                     | 0              | 0  | 1              |

| 10      | 1 | 0      | 1      | 0 | 1              | 0                     | 0              | 0  | 0              |

| 11      | 1 | 0      | 1      | 1 | 1              | 0                     | 0              | 0  | 1              |

| 12      | 1 | 1      | 0      | 0 | 1              | 0                     | 0              | 1  | 0              |

| 13      | 1 | 1      | 0      | 1 | 1              | 0                     | 0              | 1  | 1              |

| 14      | 1 | 1      | 1      | 0 | 1              | 0                     | 1              | 0  | 0              |

| 15      | 1 | 1      | 1      | 1 | 1              | 0                     | 1              | 0  | 1              |

#### K-map:

<u>BCD Code</u> — B<sub>0</sub>= A

$B_1 = DCB' + D'B$

$B_2 = D'C + CB$

\*\*\*\*\*

**DECODERS AND ENCODERS**

# Decoder:

# Explain about decoders with necessary diagrams.

(Apr 2018)(Nov 2018)

- ✤ A decoder is a combinational circuit that converts binary information from n input lines to a maximum of 2<sup>n</sup> unique output lines. If the n -bit coded information has unused combinations, the decoder may have fewer than 2<sup>n</sup> outputs.

- \* The purpose of a decoder is to generate the  $2^n$  (or fewer) minterms of *n* input variables, shown below for two input variables.

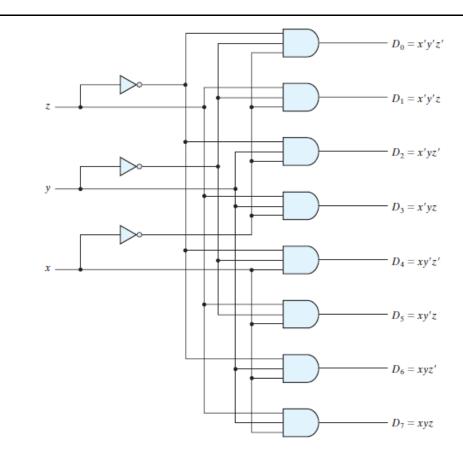

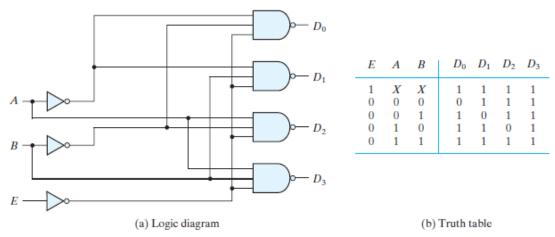

# 2 to 4 decoder:

| E | Α | В | $D_0$ | $D_1$ | $D_2$ | $D_3$ |

|---|---|---|-------|-------|-------|-------|

|   | X | Х | 1     | 1     | 1     | 1     |

| 0 | 0 | 0 | 0     | 1     | 1     | 1     |

| 0 | 0 | 1 | 1     | 0     | 1     | 1     |

| 0 | 1 | 0 | 1     | 1     | 0     | 1     |

| 0 | 1 | 1 | 1     | 1     | 1     | 1     |

(b) Truth table

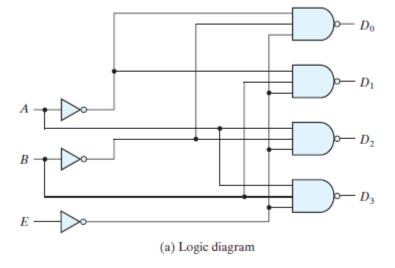

#### 3 to 8 Decoder:

Design 3 to 8 line decoder with necessary diagram. Truth table:

May -10)

| Inputs |   | Outputs |    |                |                |                       |                |                |                       |   |

|--------|---|---------|----|----------------|----------------|-----------------------|----------------|----------------|-----------------------|---|

| x      | y | z       | Do | D <sub>1</sub> | D <sub>2</sub> | <b>D</b> <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | <b>D</b> <sub>6</sub> | D |

| 0      | 0 | 0       | 1  | 0              | 0              | 0                     | 0              | 0              | 0                     | 0 |

| 0      | 0 | 1       | 0  | 1              | 0              | 0                     | 0              | 0              | 0                     | 0 |

| 0      | 1 | 0       | 0  | 0              | 1              | 0                     | 0              | 0              | 0                     | 0 |

| 0      | 1 | 1       | 0  | 0              | 0              | 1                     | 0              | 0              | 0                     | 0 |

| 1      | 0 | 0       | 0  | 0              | 0              | 0                     | 1              | 0              | 0                     | 0 |

| 1      | 0 | 1       | 0  | 0              | 0              | 0                     | 0              | 1              | 0                     | 0 |

| 1      | 1 | 0       | 0  | 0              | 0              | 0                     | 0              | 0              | 1                     | 0 |

| 1      | 1 | 1       | 0  | 0              | 0              | 0                     | 0              | 0              | 0                     | 1 |

#### Logic diagram:

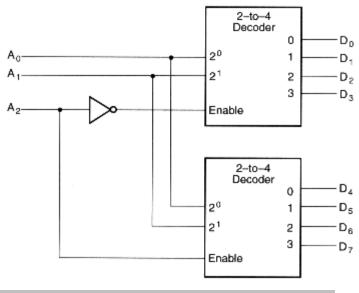

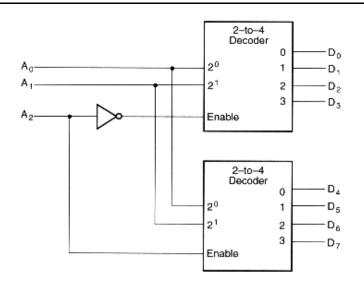

#### Design for 3 to 8 decoder with 2 to 4 decoder:

Not that the two to four decoder design shown earlier, with its *enable* inputs can be used to build a three to eight decoder as follows.

#### Implementation of Boolean function using decoder:

Since the three to eight decoder provides all the minterms of three variables, the realisation of a function in terms of the sum of products can be achieved using a decoder and OR gates as follows.

#### Example: Implement full adder using decoder.

Sum is given by  $\sum m(1, 2, 4, 7)$  while Carry is given by  $\sum m(3, 5, 6, 7)$  as given by the minterms each of the OR gates are connected to.

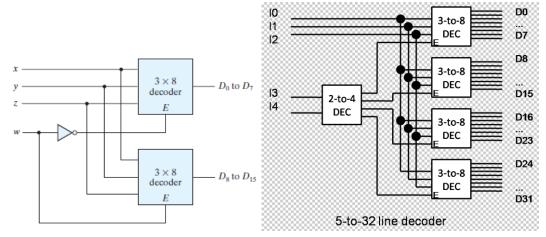

Design for 4 to 16 decoder using 3 to 8 decoder: Design 5 to 32 decoder using 3 to 8 and 2 to 4 decoder:

\*\*\*\*\*\*\*\*\*\*

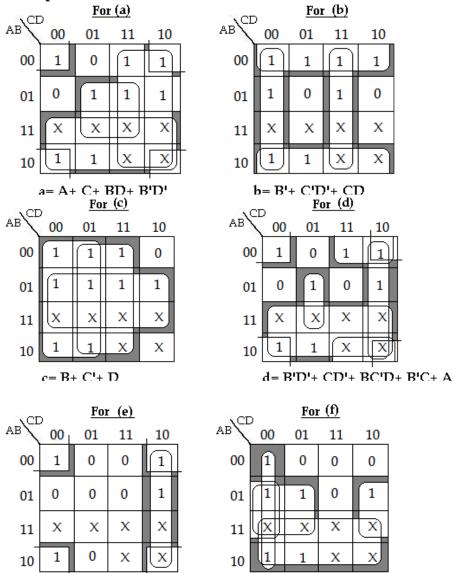

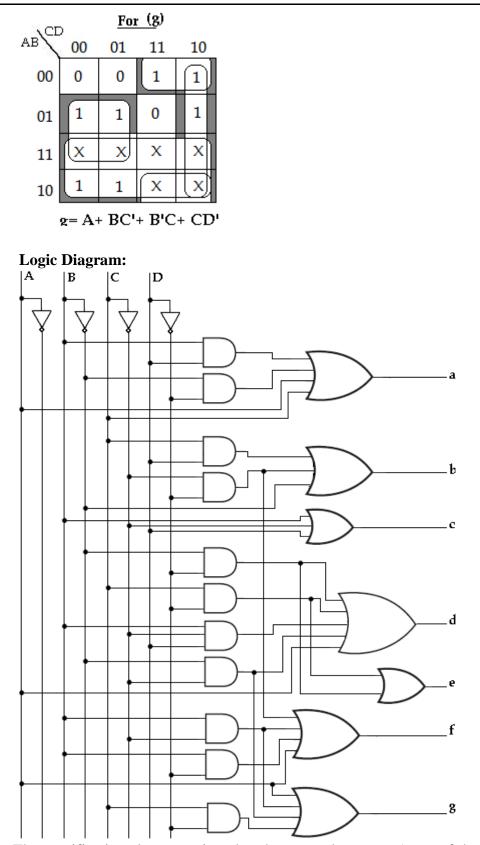

#### **BCD** to seven segment decoder

Design a BCD to seven segment code converter.

(a) Segment designation

0 823456789

(May-06,10, Nov- 09)

(b) Numeric designation for display

Truth table:

Page 33

|       | BCD code |   |   |   | 7-Segment code |   |   |   |   |   |   |  |

|-------|----------|---|---|---|----------------|---|---|---|---|---|---|--|

| Digit | Α        | В | С | D | a              | ь | с | d | e | f | g |  |

| 0     | 0        | 0 | 0 | 0 | 1              | 1 | 1 | 1 | 1 | 1 | 0 |  |

| 1     | 0        | 0 | 0 | 1 | 0              | 1 | 1 | 0 | 0 | 0 | 0 |  |

| 2     | 0        | 0 | 1 | 0 | 1              | 1 | 0 | 1 | 1 | 0 | 1 |  |

| 3     | 0        | 0 | 1 | 1 | 1              | 1 | 1 | 1 | 0 | 0 | 1 |  |

| 4     | 0        | 1 | 0 | 0 | 0              | 1 | 1 | 0 | 0 | 1 | 1 |  |

| 5     | 0        | 1 | 0 | 1 | 1              | 0 | 1 | 1 | 0 | 1 | 1 |  |

| 6     | 0        | 1 | 1 | 0 | 1              | 0 | 1 | 1 | 1 | 1 | 1 |  |

| 7     | 0        | 1 | 1 | 1 | 1              | 1 | 1 | 0 | 0 | 0 | 0 |  |

| 8     | 1        | 0 | 0 | 0 | 1              | 1 | 1 | 1 | 1 | 1 | 1 |  |

| 9     | 1        | 0 | 0 | 1 | 1              | 1 | 1 | 1 | 0 | 1 | 1 |  |

#### K-Map:

e = B'D' + CD'

f = A + C'D' + BC' + BD'

- The specification above requires that the output be zeroes (none of the segments are lighted up) when the input is not a BCD digit.

- In practical implementations, this may defer to allow representation of hexadecimal digits using the seven segments.

\*\*\*\*\*\*

#### Encoder:

#### Explain about encoders. (Nov 2018)

An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has 2<sup>n</sup> (or fewer) input lines and n output lines. The output lines, as an aggregate, generate the binary code corresponding to the input value.

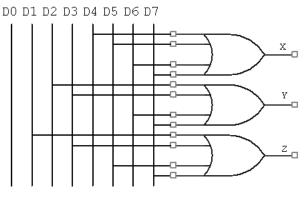

#### **Octal to Binary Encoder:**

- The encoder can be implemented with OR gates whose inputs are determined directly from the truth table. Output z is equal to 1 when the input octal digit is 1, 3, 5, or 7.

- Output y is 1 for octal digits 2, 3, 6, or 7, and output x is 1 for digits 4, 5, 6, or 7. These conditions can be expressed by the following Boolean output functions:

$z = D_1 + D_3 + D_5 + D_7$   $y = D_2 + D_3 + D_6 + D_7$  $x = D_4 + D_5 + D_6 + D_7$

The encoder can be implemented with three OR gates.

#### Truth table:

| Inputs |    |                |                |                |    |                | Outputs        |   |   |   |

|--------|----|----------------|----------------|----------------|----|----------------|----------------|---|---|---|

| Do     | D1 | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | Ds | D <sub>6</sub> | D <sub>7</sub> | x | y | z |

| 1      | 0  | 0              | 0              | 0              | 0  | 0              | 0              | 0 | 0 | 0 |

| 0      | 1  | 0              | 0              | 0              | 0  | 0              | 0              | 0 | 0 | 1 |

| 0      | 0  | 1              | 0              | 0              | 0  | 0              | 0              | 0 | 1 | 0 |

| 0      | 0  | 0              | 1              | 0              | 0  | 0              | 0              | 0 | 1 | 1 |

| 0      | 0  | 0              | 0              | 1              | 0  | 0              | 0              | 1 | 0 | 0 |

| 0      | 0  | 0              | 0              | 0              | 1  | 0              | 0              | 1 | 0 | 1 |

| 0      | 0  | 0              | 0              | 0              | 0  | 1              | 0              | 1 | 1 | 0 |

| 0      | 0  | 0              | 0              | 0              | 0  | 0              | 1              | 1 | 1 | 1 |

Another ambiguity in the octal-to-binary encoder is that an output with all 0's is generated when all the inputs are 0; but this output is the same as when D0 is equal to 1. The discrepancy can be resolved by providing one more output to indicate whether at least one input is equal to 1.

#### Logic Diagram:

\*\*\*\*\*

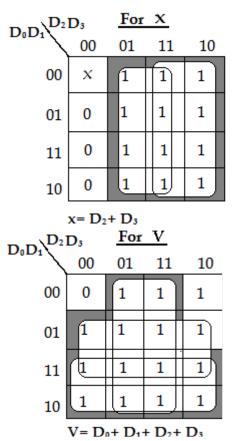

# **Priority Encoder:**

Design a priority encoder with logic diagram.(or) Explain the logic diagram of a 4 – input priority encoder. (Apr – 2019)

A priority encoder is an encoder circuit that includes the priority function. The operation of the priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

Truth table:

|    | Inputs     |                |                       | C | )utput | s |

|----|------------|----------------|-----------------------|---|--------|---|

| Do | <b>D</b> 1 | D <sub>2</sub> | <b>D</b> <sub>3</sub> | x | y      | V |

| 0  | 0          | 0              | 0                     | х | Х      | 0 |

| 1  | 0          | 0              | 0                     | 0 | 0      | 1 |

| Х  | 1          | 0              | 0                     | 0 | 1      | 1 |

| Х  | X          | 1              | 0                     | 1 | 0      | 1 |

| Х  | X          | X              | 1                     | 1 | 1      | 1 |

#### **Modified Truth table:**

|                | Inputs         |                |    |   | Output | 5 |   |

|----------------|----------------|----------------|----|---|--------|---|---|

| D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D3 | x | у      | V |   |

| 0              | 0              | 0              | 0  | x | x      | 0 |   |

| 1              | 0              | 0              | 0  | 0 | 0      | 1 |   |

| 0              | 1              | 0              | 0  | 0 | 1      | 1 |   |

| 1              | 1              | 0              | 0  | 0 | 1      | 1 |   |

| 0              | 0              | 1              | 0  |   |        |   |   |

| 0              | 1              | 1              | 0  | 1 | 1 0    | 0 | 1 |

| 0<br>1         | 0              | 1              | 0  |   | 0      | 1 |   |

| 1              | 1              | 1              | 0  |   |        |   |   |

| 0              | 0              | 0              | 1  |   |        |   |   |

| 0              | 0              | 1              | 1  |   |        |   |   |

| 0              | 1              | 0              | 1  |   |        |   |   |

| 0              | 1              | 1<br>0         | 1  | 1 | 1      | 1 |   |

| 1              | 0              | 0              | 1  |   |        |   |   |

| 1              | 0              | 1              | 1  |   |        |   |   |

| 1              | 1              | 0              | 1  |   |        |   |   |

| 1              | 1              | 1              | 1  |   |        |   |   |

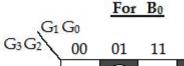

# K-Map:

| $D_0D_1$            | D3 | For |    |    |  |  |

|---------------------|----|-----|----|----|--|--|

|                     | 00 | 01  | 11 | 10 |  |  |

| 00                  | х  | 1   | 1  | 0  |  |  |

| 01                  | 1  | 1   | 1  | 0  |  |  |

| 11                  | 1  | 1   | 1  | 0  |  |  |

| 10                  | 0  | 1   | 1  | 0  |  |  |

| $y = D_3 + D_1 D_2$ |    |     |    |    |  |  |

**Logic Equations:**

$$x = D_2 + D_3$$

$$y = D_3 + D_1 D'_2$$

$$V = D_0 + D_1 + D_2 + D_3$$

Logic diagram:

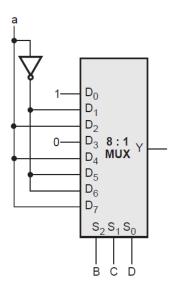

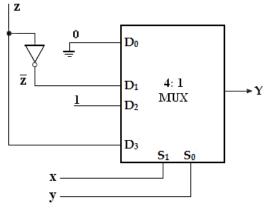

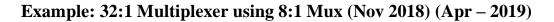

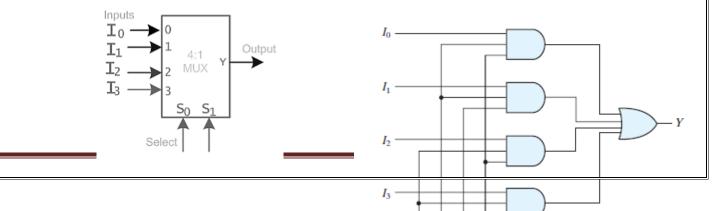

# MULTIPLEXERS AND DEMULTIPLEXERS

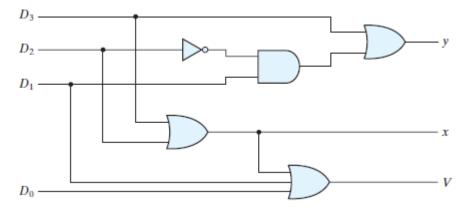

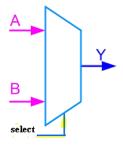

# Multiplexer: (MUX) Design a 2:1 and 4:1 multiplexer.

- A multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines.

- Normally, there are 2<sup>n</sup> input lines and n selection lines whose bit combinations determine which input is selected.

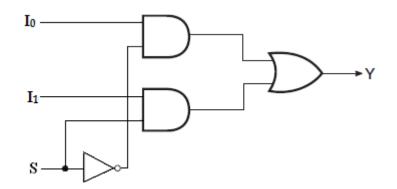

# 2 to 1 MUX:

A 2 to 1 line multiplexer is shown in figure below, each 2 input lines A to B is applied to one input of an AND gate. Selection lines S are decoded to select a particular AND gate. The truth table for the 2:1 mux is given in the table below.

To derive the gate level implementation of 2:1 mux we need to have truth table as shown in figure. And once we have the truth table, we can draw the K-map as shown in figure for all the cases when Y is equal to '1'.

# Truth table:

| S | Y              |

|---|----------------|

| 0 | Io             |

| 1 | I <sub>1</sub> |

Logic Diagram:

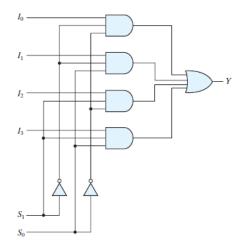

# 4 to 1 MUX:

✤ A 4 to 1 line multiplexer is shown in figure below, each of 4 input lines I0 to I3 is applied to one input of an AND gate.

- Selection lines S0 and S1 are decoded to select a particular AND gate.

- $\clubsuit$  The truth table for the 4:1 mux is given in the table below.

# **Truth Table:**

| INPUT      |    | OUTPUT |

|------------|----|--------|

| <b>S</b> 1 | S0 | Y      |

| 0          | 0  | IO     |

| 0          | 1  | I1     |

| 1          | 0  | I2     |

| 1          | 1  | I3     |

# Problems :

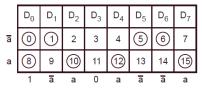

Example: Implement the Boolean expression using MUX  $F(A,B,C,D) = \sum m(0,1,5,6,8,10,12,15)$

(Apr 2017, Nov 2017)

Solution : Implementation table :

Example: Implement the boolean function using Multiplexer. [NOV – 2019]

F (x, y, z) =  $\Sigma$ m (1, 2, 6, 7)

#### Solution: Implementation table:

|   | Do | D1 | <b>D</b> 2 | <b>D</b> 3 |

|---|----|----|------------|------------|

| ī | 0  | 1  | 2          | 3          |

| z | 4  | 5  | 6          | 7          |

|   | 0  | ī  | 1          | z          |

Multiplexer Implementation:

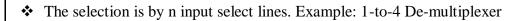

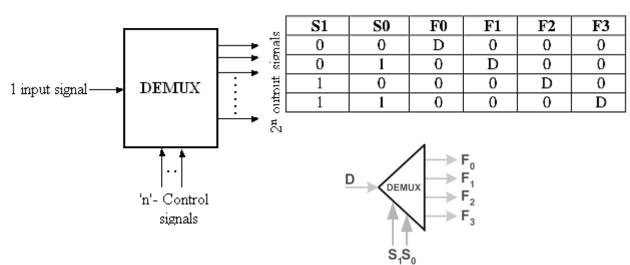

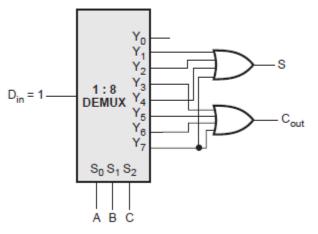

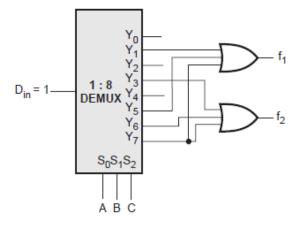

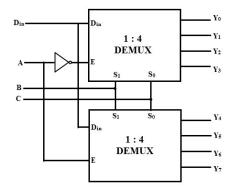

#### **DEMULTIPLEXERS:**

Explain about demultiplexers.

The de-multiplexer performs the inverse function of a multiplexer, that is it receives information on one line and transmits its onto one of 2n possible output lines.

# Truth table

# Logic Diagram:

**Truth Table:**

| INPUT |   |    |    | OUT | PUT |    |    |

|-------|---|----|----|-----|-----|----|----|

| E     | D | SO | S1 | Y0  | Y1  | Y2 | Y3 |

| 1     | 1 | 0  | 0  | 1   | 0   | 0  | 0  |

| 1     | 1 | 0  | 1  | 0   | 1   | 0  | 0  |

| 1     | 1 | 1  | 0  | 0   | 0   | 1  | 0  |

| 1     | 1 | 1  | 1  | 0   | 0   | 0  | 1  |

# **Example:**

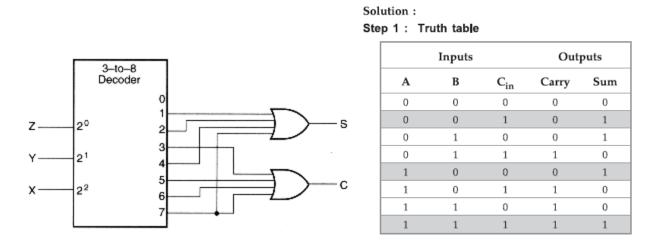

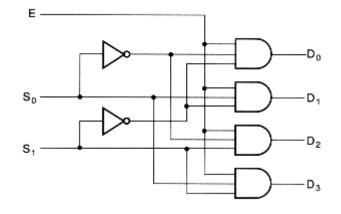

1. Implement full adder using De-multiplexer.

#### Solution : Step 1 : Truth table

|   | Inputs |     |       | puts |

|---|--------|-----|-------|------|

| Α | В      | Cin | Carry | Sum  |

| 0 | 0      | 0   | 0     | 0    |

| 0 | 0      | 1   | 0     | 1    |

| 0 | 1      | 0   | 0     | 1    |

| 0 | 1      | 1   | 1     | 0    |

| 1 | 0      | 0   | 0     | 1    |

| 1 | 0      | 1   | 1     | 0    |

| 1 | 1      | 0   | 1     | 0    |

| 1 | 1      | 1   | 1     | 1    |

Step 2: For full adder Carry =  $C_{out} = \sum m (3, 5, 6, 7)$ and Sum =  $S = \sum m (1, 2, 4, 7)$

Step 3 : When D<sub>in</sub> =1, the demultiplexer gives minterms at the output.

2. Implement the following functions using de-multiplexer. f1 (A,B,C) =  $\sum m(1,5,7)$ , f2 (A,B,C) =  $\sum m(3,6,7)$ Solution:

\*\*\*\*\*\*\*\*

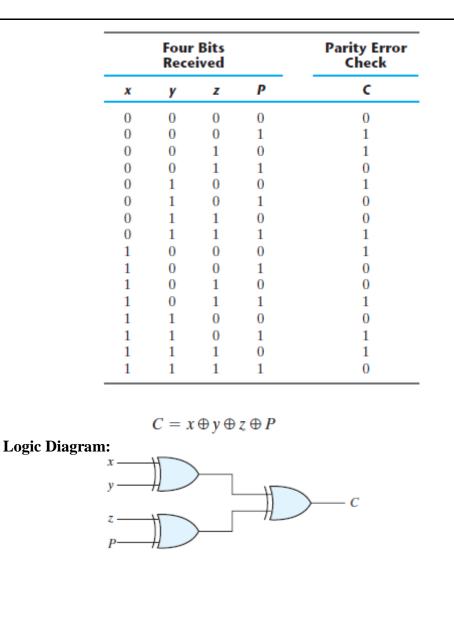

**Parity Checker / Generator:**

- A parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message, including the parity bit, is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted.

- The circuit that generates the parity bit in the transmitter is called a *parity generator*. The circuit that checks the parity in the receiver is called a *parity checker*.

- In even parity system, the parity bit is '0' if there are even number of 1s in the data and the parity bit is '1' if there are odd number of 1s in the data.

- In odd parity system, the parity bit is '1' if there are even number of 1s in the data and the parity bit is '0' if there are odd number of 1s in the data.

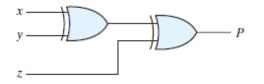

# **3-bit Even Parity generator:** Truth Table:

| Three-Bit Message |   |   | Parity Bit |

|-------------------|---|---|------------|

| x                 | y | z | Р          |

| 0                 | 0 | 0 | 0          |

| 0                 | 0 | 1 | 1          |

| 0                 | 1 | 0 | 1          |

| 0                 | 1 | 1 | 0          |

| 1                 | 0 | 0 | 1          |

| 1                 | 0 | 1 | 0          |

| 1                 | 1 | 0 | 0          |

| 1                 | 1 | 1 | 1          |

$P = x \oplus y \oplus z$

# Logic Diagram:

4-bit Even parity checker: Truth Table:

# INTRODUCTION TO HDL

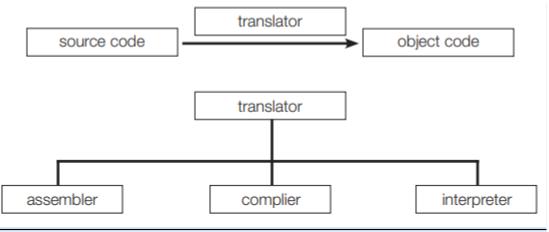

- In electronics, a hardware description language or HDL is any language from a class of computer languages and/or programming languages for formal description of digital logic and electronic circuits.

- ✤ HDLs are used to write executable specifications of some piece of hardware.

- ✤ A simulation program, designed to implement the underlying semantics of the language statements, coupled with simulating the progress of time, provides the hardware designer with the ability to model a piece of hardware before it is created physically.

- Logic synthesis is the process of deriving a list of components and their interconnection (called net list) from the model of a digital system.

- Logic Simulation is the representation of the structure and behavior of a digital logic synthesis through the use of a computer.

- $\clubsuit$  The standard HDLs that supported by IEEE.

- ✓ VHDL (very High Speed Integrated Circuit HDL)

- ✓ Verilog HDL

# HDL MODELS OF COMBINATIONAL CIRCUITS

The Verilog HDL model of a combinational circuit can be described in any one of the following modeling styles,

- ✓Gate level modeling-using instantiations of predefined and user defined primitive gates.

- ✓ Dataflow modeling using continuous assignment with the keyword **assign**.

- ✓ Behavioral modeling using procedural assignment statements with the keyword **always**.

# Gate level modeling

In this type, a circuit is specified by its logic gates and their interconnections. Gate level modeling provides a textual description of a schematic diagram. The verilog HDL includes 12basic gates as predefined primitives. They are and, nand, or, nor, xor, xnor, not & buf.

# HDL

```

// Gate-level description of two-to-four-line decoder

// Refer to Fig. 4.19 with symbol E replaced by enable, for clarity.

module decoder 2x4 gates (D, A, B, enable);

[0:3]

D:

output

A. B:

input

input

enable:

wire

A_not, B_not, enable_not;

not

G1 (A not, A).

G2 (B not, B),

G3 (enable_not, enable);

nand

G4 (D[0], A not, B not, enable not).

G5 (D[1], A not, B, enable not).

G6 (D[2], A, B_not, enable_not).

G7 (D[3], A, B, enable not);

endmodule

```

#### Data flow modeling

Data flow modeling of combinational logic uses a number of operators that act on operands to produce desired results. Verilog HDL provides about 30 different operators. Data flow modeling uses continuous assignments and the keyword **assign**. A continuous assignment is a statement that assigns a value to a net. The data type family **net** is used to represent a physical connection between circuit elements.

# HDL for2-to-4 line decoder

| Symbol | Operation          | module deco   | oder_2x4_df(                 |

|--------|--------------------|---------------|------------------------------|

|        | operation          | output        | [0: 3] D,                    |

| +      | binary addition    | input         | A, B,                        |

| -      | binary subtraction |               | enable                       |

| 8c     | bitwise AND        | );            |                              |

| 1      | bitwise OR         |               |                              |

| Λ.     | bitwise XOR        | assign        | D[0] = ~(~A & ~B & ~enable), |

| ~      | bitwise NOT        | ussign        | D[1] = -(-A & B & -enable),  |

|        | equality           |               | D[2] = -(A & -B & -enable).  |

| >      | greater than       |               | D[3] = ~(A & B & ~enable);   |

| <      | less than          | endmodule     |                              |

| { }    | concatenation      | A 1010600 008 |                              |

| ?:     | conditional        |               |                              |

#### Some Verilog HDL Operators

- Behavioral modeling represents digital circuits at a functional and algorithmic level. It is used mostly to describe sequential circuits, but can also be used to describe combinational circuits.

- Behavioral descriptions use the keyword always, followed by an optional event control expression and a list of procedural assignment statements.

// Behavioral description of two-to-one-line multiplexer

```

module mux_2x1_beh (m_out, A, B, select);

output m_out;

input A, B, select;

reg m_out;

always @(A or B or select)

if (select == 1) m_out = A;

else m_out = B;

endmodule

```

# UNIT II COMBINATIONAL LOGIC

# **TWO MARK QUESTIONS & ANSWERS**

#### 1) Define combinational logic. (May 2008, 2016)

A combinational circuit consists of logic gates whose outputs at any time are determined from only the

present combination of inputs. A combinational circuit performs an operation that canbe specified logically by a set of Boolean functions.

#### 2) What are sequential circuits?

Sequential circuits employ storage elements in addition to logic gates. Their outputs are a function of the inputs and the state of the storage elements. Because the state of the storage elements is a function of previous inputs, the outputs of a sequential circuit depend not only on present values of inputs, but also on past inputs, and the circuit behavior must be specified by a time sequence of inputs and internal states.

#### 3) Write the design procedure for combinational circuits?

The procedure involves the following steps:

1. From the specifications of the circuit, determine the required number of inputs and outputs and assign a symbol to each.

2. Derive the truth table that defines the required relationship between inputs and outputs.

3. Obtain the simplified Boolean functions for each output as a function of the input variables.

4. Draw the logic diagram and verify the correctness of the design (manually or by simulation).

#### 4) What is Half adder?

A half-adder is an arithmetic circuit block that can be used to add two bits and produce two outputs SUM and CARRY.

The Boolean expressions for the SUM and CARRY outputs are given by the equations

SUM

$$S = A.\overline{B} + \overline{A}.B$$

CARRY  $C = A.B$

#### **Truth Table:**

| А | В | s | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

5) Draw the logic diagram of half adder using NAND gate. (May 2006,13)

# Logic Diagram:Half adder using NAND gate: $A \rightarrow B \rightarrow B \rightarrow C = A.B$ $A \rightarrow C = A.B$

# 6) What is Full adder? Draw the truth table of full adder. (Apr 2018)

A Full-adder is an arithmetic circuit block that can be used to add three bits and produce two outputs SUM and CARRY.

The Boolean expressions for the SUM and CARRY outputs are given by the equations

$$\begin{split} S = \overline{A}.\overline{B}.C_{\text{in}} + \overline{A}.B.\overline{C}_{\text{in}} + A.\overline{B}.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \\ C_{\text{out}} = B.C_{\text{in}} + A.B + A.C_{\text{in}} \end{split}$$

| Α | В | Cin | SUM (S) | Cout |  |

|---|---|-----|---------|------|--|

| 0 | 0 | 0   | 0       | 0    |  |

| 0 | 0 | 1   | 1       | 0    |  |

| 0 | 1 | 0   | 1       | 0    |  |

| 0 | 1 | 1   | 0       | 1    |  |

| 1 | 0 | 0   | 1       | 0    |  |

| 1 | 0 | 1   | 0       | 1    |  |

| 1 | 1 | 0   | 0       | 1    |  |

| 1 | 1 | 1   | 1       | 1    |  |

7) Draw the Logic diagram of full adder.

#### 8) What is Half subtractor? (May 2005)

A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output. The BORROW output here specifies whether a '1' has been borrowed to perform the subtraction. The Boolean expression for difference and borrow is:

$$D = \overline{A}.B + A.\overline{B}$$

$$B_0 = \overline{A}.B$$

Page 49

Logic diagram:

# 9) Draw Full adder using Two half adder. (Apr – 2019)

#### 10) What is Full subtractor? Write the truth table of full subtractor. (Nov 2017)

A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a '1' has already been borrowed by the previous adjacent lower minuend bit or not. As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin . There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo. The BORROW output bit tells whether the minuend bit needs to borrow a '1' from the next possible higher minuend bit. The Boolean expression for difference and barrow is:

$$D = \overline{A}.\overline{B}.B_{in} + \overline{A}.B.\overline{B}_{in} + A.\overline{B}.\overline{B}_{in} + A.B.B_{in}$$

$$B_{o} = \overline{A}.B + \overline{A}.B_{in} + B.B_{in}$$

|        | Minuend<br>(A) | Subtrahend<br>(B) | Borrow<br>In (B <sub>in</sub> ) | Difference<br>(D) | Borrow<br>Out (B <sub>0</sub> ) |

|--------|----------------|-------------------|---------------------------------|-------------------|---------------------------------|

|        | 0              | 0                 | 0                               | 0                 | 0                               |

|        | 0              | 0                 | 1                               | 1                 | 1                               |

| A      | 0              | 1                 | 0                               | 1                 | 1                               |

| B Full | 0              | 1                 | 1                               | 0                 | 1                               |

| Bin    | 1              | 0                 | 0                               | 1                 | 0                               |

|        | 1              | 0                 | 1                               | 0                 | 0                               |

|        | 1              | 1                 | 0                               | 0                 | 0                               |

|        | 1              | 1                 | 1                               | 1                 | 1                               |

# 11) Draw Full subtractor using two half subtractor.

# 12) What is Parallel Binary Adder (Ripple Carry Adder)?

A binary adder is a digital circuit that produces the arithmetic sum of two binary numbers. It can beconstructed with full adders connected in cascade, with the output carryfrom each full adder connected to the input carry of the next full adder in the chain.

#### 13) Draw the logic diagram for four bit binary parallel adder.

# 14) What is 1's complement of a number?

The 1's complement of a binary number is formed by changing 1 to 0 and 0 to 1.

# Example:

- 1. The 1's complement of 1011000 is 0100111.

- 2. The 1's complement of 0101101 is 1010010.

# 15) What is 2's complement of a number?

The 2's complement of a binary number is formed by adding 1 with 1's complement of a binary number.

#### **Example:**

- 1) The 2's complement of 1101100 is 0010100

- 2) The 2's complement of 0110111 is 1001001

# 16) How Subtraction of binary numbers perform using 2's complement addition?

- $\checkmark$  The subtraction of unsigned binary number can be done by means of complements.

- $\checkmark$  Subtraction of A-B can be done by taking 2's complement of B and adding it to A.

- $\checkmark$  Check the resulting number. If carry present, the number is positive and remove the carry.

- ✓ If no carry present, the resulting number is negative, take the 2's complement of result and put negative sign.

#### 17) Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction

(a) X - Y and (b) Y - X by using 2's complements.

# Solution:

(c) X = 1010100

2's complement of Y = +0111101

Sum= 10010001

Discard end carry. Answer: X - Y = 0010001

(d) Y = 1000011

2's complement of X = +0101100

```

Sum= 1101111

```

There is no end carry. Therefore, the answer is Y - X = -(2's complement of 1101111) = -0010001.

# 18) Draw the logic diagram of Parallel Binary Subtractor.

19) Draw 1:8 Demux using two 1:4 demux. (Nov 2018)

20) Draw the logic diagram of 2's complement adder/subtractor. (May 2013)

The mode input *M* controls the operation. When M = 0, the circuit is an adder, and when M = 1, the circuit becomes a subtractor.

# 21) What is Magnitude Comparator? [NOV - 2019]

The comparison of two numbers is an operation that determines whether one number is greater than, less than, or equal to the other number. A magnitude comparator is a combinational circuit that compares two numbers A and B and determines their relative magnitudes.

The outcome of the comparison is specified by three binary variables that indicate whether A > B, A = B, or A < B.

#### 22) Design a 1-bit Magnitude Comparator.

# Truth table:

| Inpu | its | Outputs |       |       |

|------|-----|---------|-------|-------|

| В    | Α   | A > B   | A = B | A < B |

| 0    | 0   | 0       | 1     | 0     |

| 0    | 1   | 1       | 0     | 0     |

| 1    | 0   | 0       | 0     | 1     |

| 1    | 1   | 0       | 1     | 0     |

|      |     |         |       |       |

#### **Logic Circuits:**

#### 23) What is Decoder? What are binary decoders? (Nov 2017)

A decoder is a combinational circuit that converts binary information from n input lines to a maximum of  $2^n$  unique output lines. If the n -bit coded information hasunused combinations, the decoder may have fewer than  $2^n$  outputs.

The purpose of a decoder is to generate the  $2^n$  (or fewer) minterms of *n* input variables, shown below for two input variables.

#### 24) Design a 3 to 8 decoder with 2 to 4 decoder.

Not that the two to four decoder design shown earlier, with its *enable* inputs can be used to build a three to eight decoder as follows.

#### 25) What is Encoder? (May 2012)

An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has  $2^n$  (or fewer) input lines and n output lines. The output lines, as an aggregate, generate the binary code corresponding to the input value.

#### 26) What is Priority Encoder? (Apr 2017)

A priority encoder is an encoder circuit that includes the priority function. The operation of the priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

#### 27) Define Multiplexer (MUX) (or) Data Selector. (Dec 2006, May 2011) [NOV - 2019]

A multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally, there are  $2^n$  input lines and n selection lines whose bit combinations determine which input is selected.

#### 28) What is De-multiplexer?

The de-multiplexer performs the inverse function of a multiplexer, that is it receives information on one line and transmits its onto one of  $2^n$  possible output lines. The selection is by *n* input select lines.

#### 29) What is Parity?

A parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message, including the parity bit, is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted.

# **30) What is Parity Checker / Generator:**

The circuit that generates the parity bit in the transmitter is called a *parity generator*. The circuit that checks the parity in the receiver is called a *parity checker*.

# 31) What is even parity and odd parity?

In even parity system, the parity bit is '0' if there are even number of 1s in the data and the parity bit is '1' if there are odd number of 1s in the data.

In odd parity system, the parity bit is '1' if there are even number of 1s in the data and the parity bit is '0' if there are odd number of 1s in the data.

# **31)** Give the applications of Demultiplexer.

i) It finds its application in Data transmission system with error detection.

ii) One simple application is binary to Decimal decoder.

#### 32) Mention the uses of Demultiplexer.

Demultiplexer is used in computers when a same message has to be sent to different receivers. Not only in computers, but any time information from one source can be fed to several places.

#### 33) Give other name for Multiplexer and Demultiplexer.

Multiplexer is otherwise called as Data selector.

Demultiplexer is otherwise called as Data distributor.

#### 34) What is the function of the enable input in a Multiplexer?

The function of the enable input in a MUX is to control the operation of the unit.

#### 35) List out the applications of decoder? (Dec 2006)

- a. Decoders are used in counter system.

- b. They are used in analog to digital converter.

- c. Decoder outputs can be used to drive a display system.

#### 36) What is the Application of Mux?

- 1. They are used as a data selector to select one output of many data inputs.

- 2. They can be used to implement combinational logic circuits

- 3. They are used in time multiplexing systems.

- 4. They are used in frequency multiplexing systems.

- 5. They are used in A/D & D/A Converter.

- 6. They are used in data acquisition system.

# 37) List out the applications of comparators?

a. Comparators are used as a part of the address decoding circuitry in computers to select a specific input/output device for the storage of data.

b. They are used to actuate circuitry to drive the physical variable towards the reference value.

c. They are used in control applications.

# 38) What is carry look-ahead addition?

The speed with which an addition is performed limited by the time required forthe carries to propagate or ripple through all of the stage of the adder. One method ofspeeding up the process is by eliminating the ripple carry delay.

# **39) What is the Difference between Decoder & Demux.?**

| S.No | Decoder                                     | Demux                                                                                |

|------|---------------------------------------------|--------------------------------------------------------------------------------------|

| 1    | Decoder is a many inputs to many<br>Outputs | Demux is a single input to many outputs                                              |

| 2    | There are no selection lines.               | The selection of specific output line is controlled by the value of selection lines. |

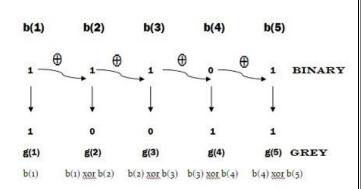

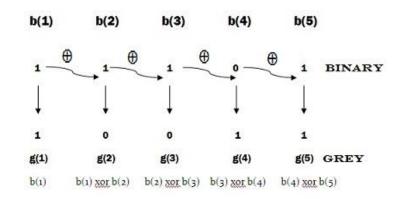

# 40) How Binary to Gray Code Conversion done?

Consider b1, b2, b3, b4 and b5 is the Binary Number and it is need be converted into Grey Code.

1. Write Most Significant Bit (MSB) is same as the MSB in Binary Number.

2. The second bit of the Grey code can be found by performing the Exclusive-OR (EX-OR) operation between the First and second bits of the Binary Number.

3. The Third bit of the Grey code can be found by performing the Exclusive-OR (EX-OR) operation between the Third and Second bits of the given Binary Number; and so on

EX-OR Operation:

- 1. Both the bits are 0 or 1 then the output of EX-OR gate will be 0.

- 2. Any one of the bit in two bits is 1 then the output of EX-OR gate will be 1.

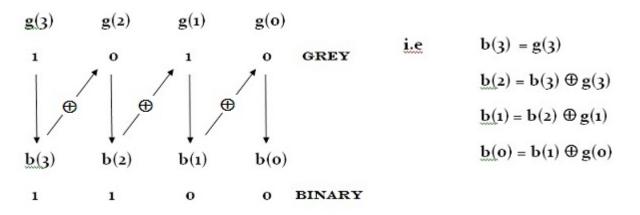

#### 41) How Gray Code to Binary Conversion done?

Consider g0, g1, g2 and g3 is the Gray Code and it is need be converted into Binary Number. The steps for Binary to Gray Code Conversion needs to be reversed to find out the equivalent Binary Number

1. The Most Significant Bit (MSB) of the Binary is same as the First MSB of the Gray Code.

2. If the second Gray Bit is 0 then the second bit of the Binary is bit will be same as that of the First Binary bit; if the Second Gray Bit is 1 then the Second Bit of the Binary will be inverse of its previous binary bit. Refer the below image for easy understanding of Gray to Binary Conversion

32) Draw the circuit for 4 to 1 line multiplexer. (Apr 2017) [NOV – 2019] Logic Diagram:

# **Truth Table:**

|    | LECT<br>PUT | OUTPUT |

|----|-------------|--------|

| S1 | S0          | Y      |

| 0  | 0           | IO     |

| 0  | 1           | I1     |

| 1  | 0           | I2     |

| 1  | 1           | I3     |

# 42) What do you meant by HDL?

Hardware description language (HDL)- hardware description language or HDL is any language from a class of computer languages and/or programming languages for formal description of digital logic and electronic circuits.

# 43) List the Verilog HDL model of a combinational circuits.

✓Gate level modeling-using instantiations of predefined and user defined primitive gates.

✓ Dataflow modeling using continuous assignment with the keyword **assign**.

✓ Behavioral modeling using procedural assignment statements with the keyword **always**.

# 44) What is meant by Gate level modeling?

In this type, a circuit is specified by its logic gates and their interconnections. Gate level modeling provides a textual description of a schematic diagram.

# 45) What is meant by data flow modeling?

Data flow modeling of combinational logic uses a number of operators that act on operands to produce desired results. Verilog HDL provides about 30 different operators.

# 46) What is meant by Behavioral modeling?

Behavioral modeling represents digital circuits at a functional and algorithmic level. It is used mostly to describe sequential circuits, but can also be used to describe combinational circuits.

#### 47) What is Verilog?

Verilog is a general purpose hardware descriptor language. It has similar in syntax to the C programming language. It can be used to model a digital system at many levels of abstraction ranging from the algorithmic level to the switch level.

#### 48) Define logic synthesis and simulation.

*Logic synthesis* is the process of deriving a list of components and their interconnection (called netlist) from the model of a digital system.

*Logic Simulation* is the representation of the structure and behavior of a digital logic synthesis through the use of a computer.

# 49) List the standard HDLs that supported by IEEE.

- ✓ VHDL (very High Speed Integrated Circuit HDL)

- ✓ Verilog HDL

- 50) Write the truth table of 2 to 4 line decoder and draw its logic diagram. (Apr 2019)

- 2 to 4 decoder:

- 51) State the different modeling techniques used in HDL. (Apr 2018)

- Gate level modeling

- Data flow modeling

- Behavioral modeling

# UNIT III

# SYNCHRONOUS SEQUENTIAL LOGIC

Sequential Circuits - Storage Elements: Latches, Flip-Flops - Analysis of Clocked Sequential Circuits - State Reduction and Assignment - Design Procedure - Registers and Counters - HDL Models of Sequential Circuits

#### SEQUENTIAL CIRCUITS

#### Sequential circuits:

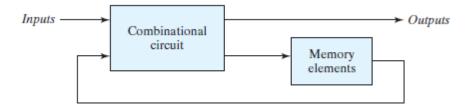

- Sequential circuits employ storage elements in addition to logic gates. Their outputs are a function of the inputs and the state of the storage elements.

- Because the state of the storage elements is a function of previous inputs, the outputs of a sequential circuit depend not only on present values of inputs, but also on past inputs, and the circuit behavior must be specified by a time sequence of inputs and internal states.

# Types of sequential circuits:

There are two main types of sequential circuits, and their classification is a function of the timing of their signals.

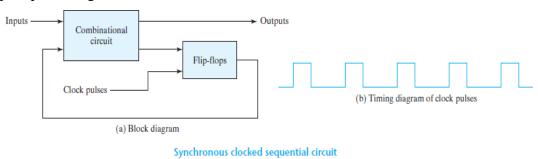

#### 1. Synchronous sequential circuit:

It is a system whose behaviorcan be defined from the knowledge of its signals at discrete instants of time.

# 2. Asynchronous sequential circuits:

The behavior f an asynchronous sequential circuit depends upon the input signals at any instant of time and the order in which the inputs change. The storage elements commonly used in asynchronous sequential circuits are time-delay devices.

# LATCHES AND FLIP FLOPS

# Flip-Flop:

- The storage elements (memory) used in clocked sequential circuits are called flipflops. A flip-flop is a binary storage device capable of storing one bit of information. In a stable state, the output of a flip-flop is either 0 or 1.

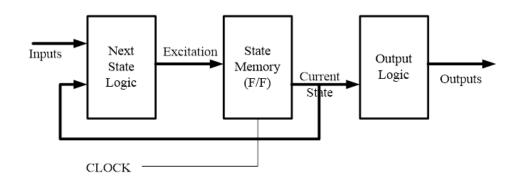

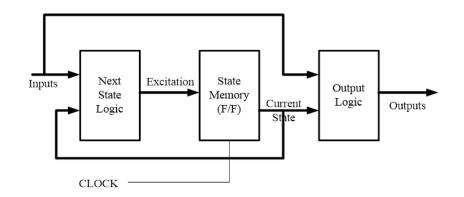

- A sequential circuit may use many flip-flops to store as many bits as necessary. The block diagram of a synchronous clocked sequential circuit is shown in Fig.

- A storage element in a digital circuit can maintain a binary state indefinitely (as long as power is delivered to the circuit), until directed by an input signal to switch states.

- The major differences among various types of storage elements are in the number of inputs they possess and in the manner in which the inputs affect the binary state.

#### Latch:

The storage elements that operate with signal levels (rather than signal transitions) are referred to as latches; those controlled by a clock transition are flip-flops.Latches are said to be level sensitive devices; flip-flops are edge-sensitive devices.

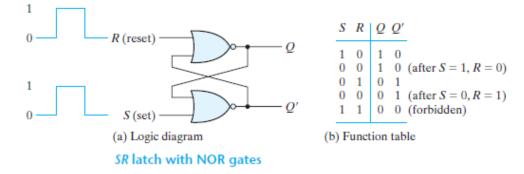

#### SR Latch: Using NOR gate

# Realize SR Latch using NOR and NAND gates and explain its operation.

- The SR latch is a circuit with two cross-coupled NOR gates or two cross-coupled NAND gates, and two inputs labeled S for set and R for reset.

- > The SR latch constructed with two cross-coupled NOR gates is shown in Fig.

- The latch has two useful states. When output Q = 1 and Q'= 0, the latch is said to be in the set state.

When Q = 0 and Q' = 1, it is in the reset state. Outputs Q and Q' are normally the complement of each other.

- However, when both inputs are equal to 1 at the same time, a condition in which both outputs are equal to 0 (rather than be mutually complementary) occurs.

- If both inputs are then switched to 0 simultaneously, the device will enter an unpredictable or undefined state or a metastable state. Consequently, in practical applications, setting both inputs to 1 is forbidden.

# FLIP FLOPS

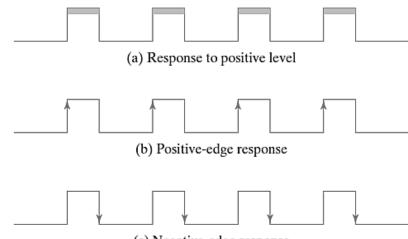

# **Triggering of Flip Flops:**

# Explain about triggering of flip flops in detail.

The state of a latch or flip-flop is switched by a change in the control input. This momentary change is called a *trigger*, and the transition it causes is said to trigger the flip-flop.

(c) Negative-edge response

# Level Triggering:

- SR, D, JK and T latches are having enable input.

- Latches are controlled by enable signal, and they are level triggered, either positive level triggered or negative level triggered as shown in figure (a).

- The output is free to change according to the input values, when active level is maintained at the enable input.

# **Edge Triggering:**

- $\blacktriangleright$  A clock pulse goes through two transitions: from 0 to 1 and the return from 1 to 0.

- As shown in above Fig (b) and (c)., the positive transition is defined as the positive edge and the negative transition as the negative edge.

\*\*\*\*\*

Explain the operation of flipflops.(Nov 2017)

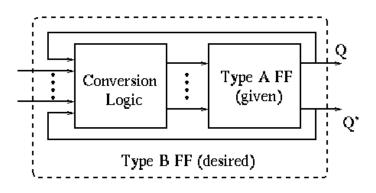

# FLIP FLOP CONVERSIONS

The purpose is to convert a given type A FF to a desired type B FF using some conversion logic.

The key here is to use the excitation table, which shows the necessary triggering signal (S,R, J,K, D and

$$Q_t \to Q_{t+1}$$

T) for a desired flipflop state transition

**Excitation table for all flip flops:**

| Qt | Q <sub>t+1</sub> | S | R | D | J | K | Т |

|----|------------------|---|---|---|---|---|---|

| 0  | 0                | 0 | X | 0 | 0 | Х | 0 |

| 0  | 1                | 1 | 0 | 1 | 1 | Х | 1 |